# **Backlight LED Boost Driver**

The NCP5008/NCP5009 is a high efficiency boost converter operating in current loop control mode to drive Light Emitting Diode. The current mode regulation allows a uniform brightness of the LEDs.

#### **Features**

- 2.7 to 6.0 V Input Voltage Range

- Output Voltage from V<sub>bat</sub> to 15 V

- 3.0 µA Quiescent Supply Current

- Automatically LEDs Current Matching

- No External Sense Resistor

- Includes Dimming Function

- Programmable or Automatic Current Output Mode

- LOCAL or REMOTE Control Facility

- Photo Transistor Sense Feedback Input

- Inductor Based Converter brings High Efficiency

- Low Noise DC/DC Converter

- All Pins are Fully ESD Protected

#### **Typical Applications**

- LED Display Back Light Control

- High Efficiency Step Up Converter

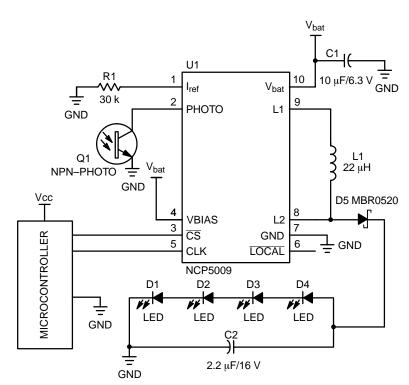

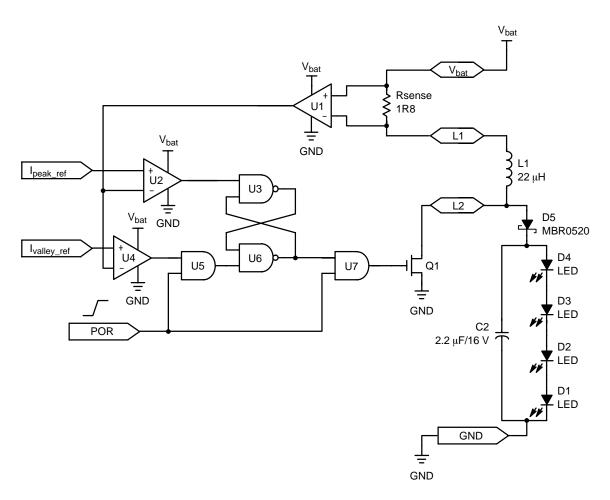

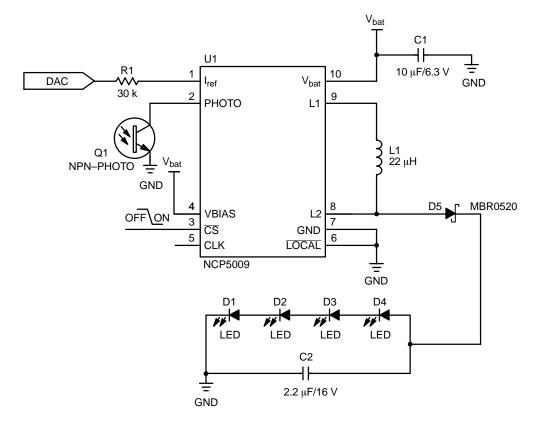

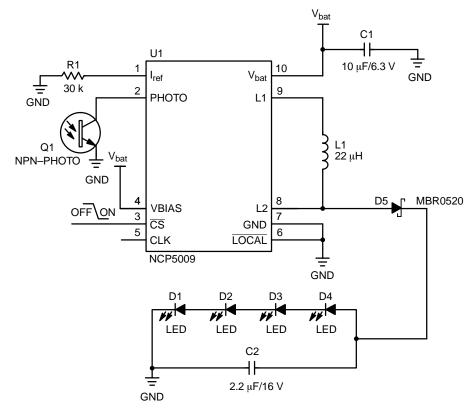

Figure 1. Typical Battery Powered LED Boost Driver

#### OIT Scillicollaucte

http://onsemi.com

Micro 10 DM SUFFIX CASE 846B

x = Device Number 8 or 9 A = Assembly Location

Y = Year

W = Work Week

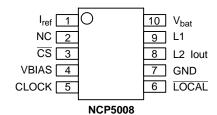

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 18 of this data sheet.

#### **BACK LIGHT WHITE LED CURRENT DRIVE CONTROLLER**

NOTE: This functionality is NOT implemented on the NCP5008 type.

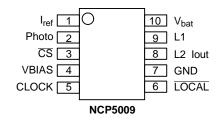

Figure 2. Block Diagram

#### PIN FUNCTION DESCRIPTION

| Pin | Symbol           | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | I <sub>ref</sub> | INPUT  | This pin provides the output current range adjustment by means of a resistor connected to ground. The current output tolerance depends upon the accuracy of this resistor. Using a $\pm 1\%$ metal film resistor, or better, yields the best output current accuracy.                                                                                                                                                                                                                                                                                                                                                               |

| 2   | РНОТО            | SIGNAL | This pin provides an access to the output current control loop for the NCP5009 version. The current sunk to ground from this pin is subtracted from the output current mirror. Primary use is the ambient light automatic adjustment by means of an external photo transistor connected across this pin and ground. The output current decreases as the ambient light increases. The internal circuit provides a 1/1 current ratio with the $I_{\text{ref}}$ defined by the resistor connected from pin 1 to ground. This current shall be limited to 65 $\mu\text{A}$ . This functionality is NOT implemented on the NCP5008 type. |

| 3   | CS               | INPUT  | Negative going Chip Select logic input. This pin is used to select the NCP5008/ NCP5009 and validate the clock/data when $\overline{\text{CS}}$ = Low. The internal shift register is automatically clear to zero upon the falling edge, thanks to a 20 ns built–in one shoot. The built–in pull–up resistor disables the device when the $\overline{\text{CS}}$ pin is left open.                                                                                                                                                                                                                                                  |

| 4   | VBIAS            | POWER  | This pin should be connected to V <sub>bat</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | CLOCK            | INPUT  | The clock signal connected to this pin is used to serially shift right the internal preset high logic level. The clock is valid between the falling edge and until the rising edge of the $\overline{\text{CS}}$ . There is neither a feedback nor an overflow control. If the clock count exceeds 8 bits, the internal register is clear, the output current is forced to zero and the device comes back to the shutdown mode.                                                                                                                                                                                                     |

| 6   | TOCAL            | INPUT  | <ul> <li>This pin is used to select the mode of operation.</li> <li>When LOCAL = High or Open, the chip is controlled by two digital lines:</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7   | GND              | POWER  | This pin is the system ground for the NCP5008/NCP5009 and carries both the Power and the Digital signals. High quality ground must be provided to avoid spikes and/or uncontrolled operation. Care must be observed to avoid high–density current flow in a limited PCB copper track.                                                                                                                                                                                                                                                                                                                                               |

| 8   | L2               | POWER  | This pin is the power side of the external inductor and must be connected either to the external Schottky diode (see Figure 22) or directly to one external LED (see Figure 23). It provides the output current to the load. Since the boost converter operates in a current loop mode, the output voltage can range up to +15 V but shall not extend this limit. The user must make sure this voltage will not be exceeded during the normal operation of this part.                                                                                                                                                               |

|     |                  |        | An external low cost ceramic capacitor (2.2 $\mu$ F/16 V, ESR < 100 m $\Omega$ ) is recommended to smooth the current flowing into the diode(s), thus limiting the noise created by the fast transients present in this circuitry.                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                  |        | Care must be observed to avoid EMI though the PCB copper tracks connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9   | L1               | POWER  | The return side of the external inductor shall be connected to this pin. Typical application will use a 22 $\mu$ H, size 1210, to handle the 2.8 to 364 mA max range. On the other hand, when the desired output current is above 20 mA, the inductor shall have an ESR < 1.0 $\Omega$ . The output current tolerance can be improved by using a larger inductor value.                                                                                                                                                                                                                                                             |

| 10  | V <sub>bat</sub> | POWER  | The external voltage supply is connected to this pin. A high quality reservoir capacitor must be connected across pin 10 and Ground to achieve the specified output voltage parameters. A 10 $\mu$ F/6.3 V, low ESR capacitor must be connected as close as possible across pin 10 and ground pin 7. The X5R ceramic types are recommended.                                                                                                                                                                                                                                                                                         |

#### **Table 1. Shift Register Bits Assignment and Functions**

**SetReg** shift register (Note: The register content is latched upon  $\overline{CS}$  positive going).

|                       | В7                      | В6                      | B5                      | B4                      | В3                      | B2                      | B1                      |

|-----------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| Bn Value<br>After POR | 0                       | 0                       | 0                       | 0                       | 0                       | 0                       | 0                       |

| lout Peak (mA)        | I <sub>ref</sub> *k*7.5 | I <sub>ref</sub> *k*6.5 | I <sub>ref</sub> *k*5.5 | I <sub>ref</sub> *k*4.5 | I <sub>ref</sub> *k*3.5 | I <sub>ref</sub> *k*2.5 | I <sub>ref</sub> *k*1.5 |

| LOCAL     | CLOCK    | CS | B1-B7             | Output Peak Current               |

|-----------|----------|----|-------------------|-----------------------------------|

| L         | Х        | Н  | X                 | 0                                 |

| L         | Х        | L  | X                 | l <sub>ref</sub> * k * 7.5        |

| H or Open | Х        | Н  | No Change         | I <sub>ref</sub> * k * (Bn + 0.5) |

| H or Open | <b>\</b> | L  | No Change         | I <sub>ref</sub> * k * (Bn + 0.5) |

| H or Open | 1        | L  | $Q_{data} \to Bn$ | I <sub>ref</sub> * k * (Bn + 0.5) |

The register is clear to zero during the first 20 ns following the  $\overline{\text{CS}}$  falling edge.

#### Note:

Coefficient Value (internal ratio): k = 746

Maximum output peak current @ B7 = 1 and Iphoto = 0  $\mu A$  : Iout peak =  $I_{ref}$  \* (7 + 0.5) \* 746 =  $I_{ref}$  \* 5595

$$I_{ref} = \frac{V_{ref}}{R1} = \frac{1.24 \text{ V}}{R1}$$

#### **MAXIMUM RATINGS**

| Rating                                                                                         | Symbol                               | Value                                      | Unit       |

|------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|------------|

| Power Supply                                                                                   | V <sub>bat</sub> , V <sub>BIAS</sub> | 7.0                                        | V          |

| Output Power Supply Voltage Compliance                                                         | $V_{L2}$                             | 16                                         | V          |

| Digital Input Voltage<br>Digital Input Current                                                 | CLK, CS                              | -0.3 < V < V <sub>bat</sub> + 3.0 V<br>1.0 | V<br>mA    |

| Human Body Model: R = 1500 Ω, C = 100 pF                                                       | ESD                                  | ±2.0                                       | kV         |

| Machine Model                                                                                  | ESD                                  | ±200                                       | V          |

| Micro 10 Package Power Dissipation @ T <sub>A</sub> = +85°C Thermal Resistance Junction–to–Air | P <sub>D</sub><br>R <sub>Thja</sub>  | 200<br>200                                 | mW<br>°C/W |

| Operating Ambient Temperature Range                                                            | T <sub>A</sub>                       | -25 to +85                                 | °C         |

| Operating Junction Temperature Range                                                           | T <sub>J</sub>                       | -25 to +125                                | °C         |

| Maximum Junction Temperature                                                                   | T <sub>Jmax</sub>                    | +150                                       | °C         |

| Storage Temperature Range                                                                      | T <sub>stg</sub>                     | -65 to +150                                | °C         |

Maximum Ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum–rated conditions is not implied. Functional operation should be restricted to the Recommended Operating Conditions.

#### POWER SUPPLY SECTION (-25°C to +85°C ambient temperature, unless otherwise noted.)

| Rating                                                                                                                                       | Pin | Symbol              | Min | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|-----|------|------|------|

| Power Supply                                                                                                                                 | 10  | V <sub>bat</sub>    | 2.7 | -    | 6.0  | V    |

| Power Supply Threshold Start Up Voltage                                                                                                      | 10  | V <sub>batThr</sub> | _   | 2.3  | 2.7  | V    |

| Output Load Voltage Compliance                                                                                                               | 8   | V <sub>out</sub>    | _   | -    | 15.0 | V    |

| Pulsed Current Regulation Range                                                                                                              | 8   | l <sub>out</sub>    | 0   | -    | 400  | mA   |

| Continuous DC Current in the Load                                                                                                            | 8   | l <sub>out</sub>    | _   | -    | 75   | mA   |

| Output Pulsed Current Tolerance @ $V_{bat}$ = 3.6 V, L1 = 22 $\mu$ H/0.71 $\Omega$ , R <sub>ref</sub> ±1%, I <sub>LED</sub> = 20 mA (Note 1) | 8   | l <sub>out</sub>    | -   | ±5.0 | -    | %    |

| Output Leakage @ LOCAL = 0, $\overline{CS}$ = H, Vout = 15 V, V <sub>bat</sub> = 6.0 V                                                       | 8   | l <sub>out</sub>    | _   | _    | 500  | nA   |

| Standby Current @ lout = 0 mA, $\overline{\text{CS}}$ = H, CLK = H, V <sub>bat</sub> = V <sub>BIAS</sub> = 3.6 V                             | 10  | I <sub>stdb</sub>   | _   | 3.0  | -    | μΑ   |

| Standby Current @ lout = 0 mA, $\overline{\text{CS}}$ = H, CLK = H, V <sub>bat</sub> = V <sub>BIAS</sub> = 6.0 V                             | 10  | I <sub>stdb</sub>   | _   | -    | 10   | μΑ   |

| Operating Current @ $V_{bat} = V_{BIAS} = 3.6 \text{ V}$ , $I_{ref} = 30 \mu\text{A}$ , $CLK = H$ , $\overline{CS} = L$ , LOCAL = Open       | 10  | I <sub>ope</sub>    | -   | 600  | -    | μΑ   |

| Boost Internal Oscillator Clock @ L1 = 22 $\mu$ H, $V_{bat}$ = $V_{BIAS}$ = 3.6 V, lout = 20 mA (Vout = 14 V)                                | -   | F <sub>osc</sub>    | -   | 300  | _    | kHz  |

<sup>1.</sup> The tolerance refers to the 20 mA to 70 mA current range.

**DIGITAL SECTION** (–25°C to +85°C ambient temperature, unless otherwise noted.)

| Rating                                              | Pin  | Symbol                                | Min                         | Тур                                              | Max                                        | Unit   |

|-----------------------------------------------------|------|---------------------------------------|-----------------------------|--------------------------------------------------|--------------------------------------------|--------|

| High Level Input Voltage<br>Low Level Input Voltage | 3, 5 | V <sub>IH</sub><br>V <sub>IL</sub>    | 0.7 * V <sub>bat</sub><br>– | -                                                | V <sub>bat</sub><br>0.3 * V <sub>bat</sub> | V<br>V |

| Input Capacitance                                   |      | C <sub>in</sub>                       | _                           | 10                                               | _                                          | pF     |

| High Level Input Voltage<br>Low Level Input Voltage | 6    | V <sub>IH</sub><br>V <sub>IL</sub>    | -<br>-                      | 0.6 * V <sub>bat</sub><br>0.4 * V <sub>bat</sub> | _<br>_                                     | V<br>V |

| Input Capacitance                                   |      | C <sub>in</sub>                       | _                           | 10                                               | _                                          | pF     |

| LOCAL Pull–up Resistor                              | 6    | R <sub>loc</sub>                      | 20                          | _                                                | 80                                         | kΩ     |

| LOCAL Leakage Current                               | 9    | I <sub>Loc</sub>                      | -                           | -                                                | 100                                        | nA     |

| CS Pull–up Resistor                                 | 3    | R <sub>cs</sub>                       | 20                          | -                                                | 80                                         | kΩ     |

| Minimum CS Low Time                                 | 3    | Tcs <sub>setup</sub>                  | 250                         | -                                                | -                                          | ns     |

| Clock Frequency                                     | 5    | F <sub>CLK</sub>                      | -                           | -                                                | 5.0                                        | MHz    |

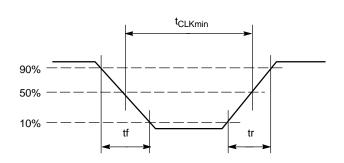

| CLOCK tr and tf                                     | 5    | tr <sub>CLK</sub> , tf <sub>CLK</sub> | 10                          | -                                                | -                                          | ns     |

| Internal Register Clear                             | _    | t <sub>clear</sub>                    | 10                          | 30                                               | _                                          | ns     |

| Internal Power on Reset Width                       | _    | t <sub>POR</sub>                      | _                           | 100                                              | _                                          | μs     |

<sup>2.</sup> Digital inputs undershoot < -0.30 V, Digital inputs overshoot < 0.30 V.

#### ANALOG SECTION (-25°C to +85°C ambient temperature, unless otherwise noted.)

| Rating                                                                         | Pin   | Symbol              | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------------------------|-------|---------------------|------|------|------|------|

| Output Voltage Range Reference<br>@ 2.5 μA < I <sub>ref</sub> < 65 μA (Note 3) | 1     | V <sub>ref</sub>    | 1.20 | 1.24 | 1.28 | V    |

| Maximum Output Current Range Ratio                                             | 8     | l <sub>out</sub>    | -    | 5595 | _    | -    |

| Minimum Output Current Range Ratio                                             | 8     | l <sub>out</sub>    | -    | 1119 | -    | -    |

| Output Current Sense Resistor                                                  | 10, 9 | R <sub>s</sub>      | -    | 1.8  | 2.2  | Ω    |

| Output Voltage Range Reference<br>@ 2.5 μA < Ipho < 65 μA                      | 2     | $V_{pho}$           | 1.20 | 1.24 | 1.28 | V    |

| Output Current Stabilization tdelay following a DC/DC start up                 | 8     | I <sub>outdly</sub> | -    | 100  | -    | μS   |

| Internal NMOS Resistor @ V <sub>bat</sub> = 3.6 V                              | 8     | QR <sub>DSON</sub>  | _    | 2.2  | 3.0  | Ω    |

| Internal Comparator Delay Time                                                 | _     | Td <sub>comp</sub>  | -    | 60   | _    | ns   |

<sup>3.</sup> The overall tolerance depends upon the accuracy of the external resistor. Using a 1%/low PPM metal film resistor is recommended to achieve  $\pm$ 5% output current tolerance.

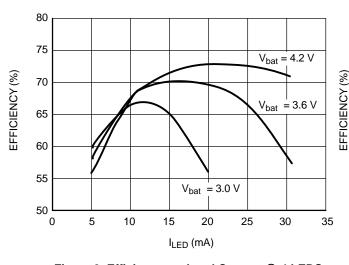

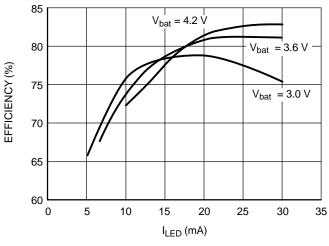

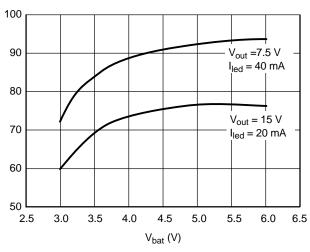

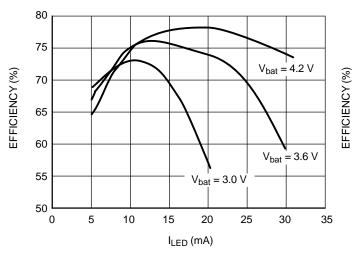

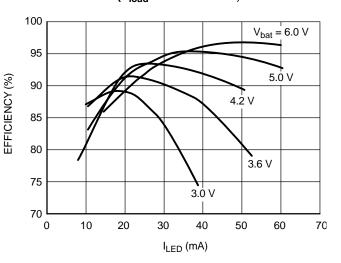

#### TYPICAL OPERATING CHARACTERISTICS

Condition: Typical Application: L = 22  $\mu$ H, Cin = 10  $\mu$ F, Cout = 2.2  $\mu$ F, R1 = 30  $k\Omega$

**EFFICIENCY (%)**

80  $V_{\text{bat}} = 4.2 \text{ V}$ 75  $V_{bat} = 3.6 V$ 70 65 60 55  $V_{bat} = 3.0 V$ 50 0 5 10 15 20 25 30 35 I<sub>LED</sub> (mA)

Figure 3. Efficiency vs. Load Current @ 4 LEDS ( $V_{load}$  = 4\*Vf  $\Rightarrow$  14.2 V)

Figure 4. Efficiency vs. Load Current @ 3 LEDS  $(V_{load} = 3*Vf \Rightarrow 10.5 V)$

Figure 5. Efficiency vs. Load Current @ 2 LEDS ( $V_{load}$  = 2\*Vf  $\Rightarrow$  7.1 V)

Figure 6. Efficiency vs.  $V_{bat}$  @  $V_{out} = 15 \text{ V/I}_{led} = 20\text{mA}$  and

Figure 7. Efficiency vs. Load Current @ 4 LEDS (V<sub>load</sub> = 2 strings of 2 LEDs in series = 7.1V)

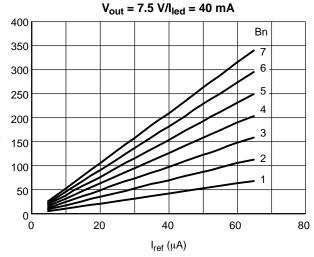

Figure 8. Inductor peak Current vs.  $I_{ref}$  @ Bn = {1, 2, 3, 4, 5, 6, 7}

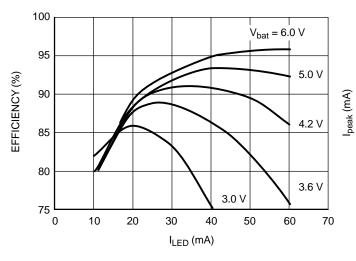

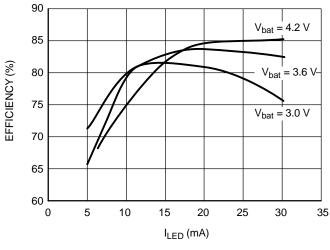

#### TYPICAL OPERATING CHARACTERISTICS

Condition: Typical Application: L = 22  $\mu H,~Cin$  = 10  $\mu F,~Cout$  = 2.2  $\mu F,~R1$  = 30  $k\Omega$

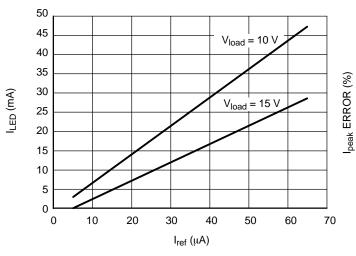

Figure 9. Load Current ( $I_{led}$ ) vs.  $I_{ref}$  @  $V_{bat}$  = 3.6 V,  $V_{load}$  = 15 V and 10 V

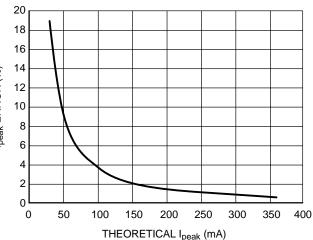

Figure 10. Inductor Peak Current Error vs.

Theoretical Inductor Peak Current

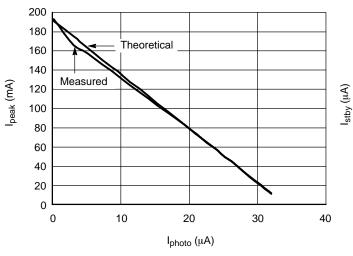

Figure 11. Inductor Peak Current vs. I $_{photo}$  @ I $_{ref}$  = 34  $\mu$ A

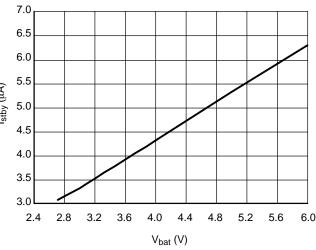

Figure 12. Stand by Current vs. V<sub>bat</sub> @ T = 20°C

#### TYPICAL OPERATING CHARACTERISTICS

Condition: Typical Application: L = 22  $\mu$ H, Cin = 10  $\mu$ F, Cout = 2.2  $\mu$ F, R1 = 30  $k\Omega$

85 80  $V_{\text{bat}} = 4.2 \text{ V}$ 75  $V_{\text{bat}} = 3.6 \text{ V}$ 70 65 60 55  $V_{\text{bat}} = 3.0 \text{ V}$ 50 0 5 10 15 20 25 30 35  $I_{\text{LED}}$  (mA)

Figure 13. Efficiency vs. Load Current @ 4 LEDS ( $V_{load}$  = 4\*Vf  $\Rightarrow$  14.2 V)

Figure 14. Efficiency vs. Load Current @ 3 LEDS  $(V_{load} = 3*Vf \Rightarrow 10.5 V)$

Figure 15. Efficiency vs Load Current @ 2 LEDS ( $V_{load}$  = 2\*Vf  $\Rightarrow$  7.1 V)

Figure 16. Efficiency vs Load Current @ 4 LEDS (V<sub>load</sub> = 2 strings of 2 LEDs in series = 7.1 V)

#### **Operating Description**

Figure 17. Digital Timing Definitions

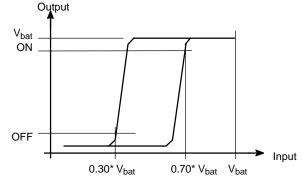

Figure 18. Typical Schmitt Trigger Characteristic

#### **Input Schmitt Triggers**

All the Logic Input pins have built—in Schmitt trigger circuits to prevent the NCP5008/NCP5009 against uncontrolled operation. The typical dynamic characteristics of the related pins are depicted in Figure 18.

The output signal is guaranteed to go High when the input voltage is above  $0.70*V_{bat}$ , and will go Low when the input voltage is below  $0.30*V_{bat}$ .

#### **ESD Protection**

The NCP5008/NCP5009 includes silicon devices to protect the pins against the ESD spikes voltages. To cope with the different ESD voltages developed in the applications, the built–in structures have been designed to handle  $\pm 2.0~\rm kV$  in Human Body Model (HBM) and  $\pm 200~\rm V$  in Machine Model (MM) and on each pin.

#### **Programming Sequence**

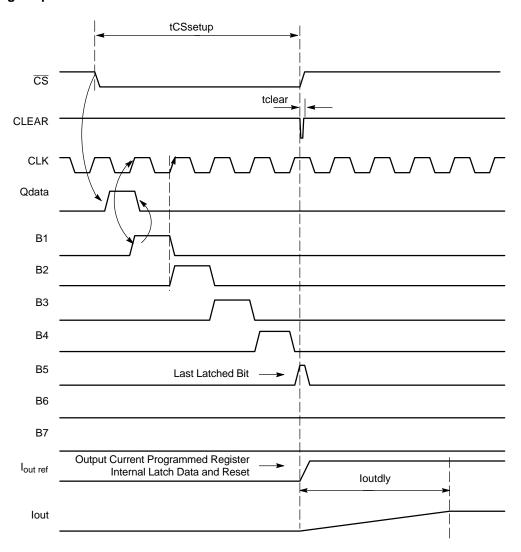

Figure 19. Programming Sequence

Upon  $\overline{CS}$  transition from High to Low, the internal sequence will take place:

- Qdata is internally set to high level.

- Upon positive going transition of the next CLK signal, the Qdata is shifted to the next Bn stage.

- Clear the Qdata flip-flop upon the positive going of the SetReg[B1] transient.

The sequence keeps going until  $\overline{CS}$  = High.

When the  $\overline{\text{CS}}$  line returns to a High state, the programming output current flip-flop is set according to the previous state of the shift register and SetReg B[1–7] is cleared afterward.

Depending upon the  $\overline{CS}$  width, for a given CLK period, the last SetReg bit will be latched and the output current

will be adjusted accordingly. If the number of CLK pulses is higher than 7, the Qdata is lost and the SetReg register bits B[1–7] are in the Low state, yielding a zero output current.

The internal shift register can be clear by sending more than 7 pulses to the CLK pin when the pin  $\overline{CS}$  is low. If the internal shift register is clear upon the  $\overline{CS}$  transition from Low to High, the device will be placed or maintained in the shut down mode.

When the register content is higher than zero, the DC/DC is activated and a  $100 \mu s$  delay (typical) is necessary to stabilize the output current to the programmed value.

#### Set Up Output Current Range

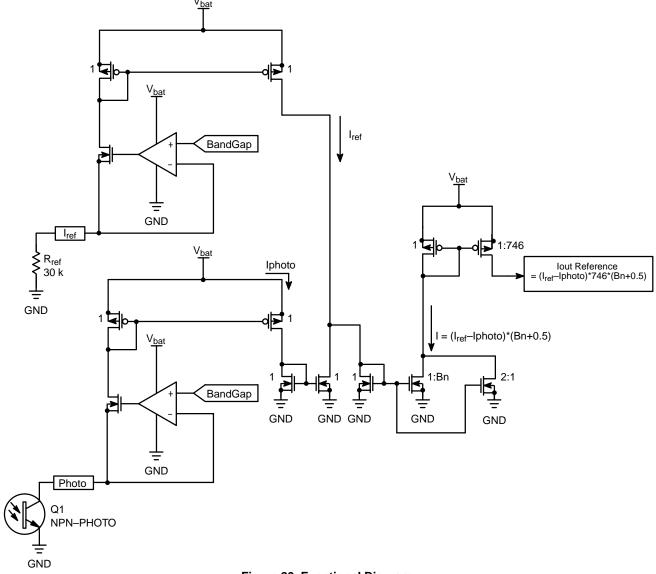

Figure 20. Functional Diagram

The current sunk to ground on PHOTO pin is subtracted from the current sunk to ground on  $I_{ref}$  pin. The result is multiplied by the programmed value (Bn) and then multiplied by the constant factor ratio (k=746) in the current mirror.

The constant factor k is a ratio between the current on Iout sense and the Iout reference internally fixed.

The output current reference is:

$Ipeak = Ivalley + (I_{ref} - Iphoto) * Bn * k.$

Where k = 746, Bn represents the bit of the internal shift register, range from 1 to 7, and Ivalley =  $(I_{ref} - Iphoto) * 0.5 * k$ .

We can write also Ipeak =  $(I_{ref} - Iphoto) * (Bn + 0.5) * k$ . Please find below the formula to quickly calculate R1 resistor (resistor on  $I_{ref}$  pin):

$$I_{ref} = \frac{1.24}{R1}$$

#### **DC/DC Converter Operation**

The DC/DC converter operates with a boost structure depicted in Figure 21, the load being supplied by the pulsed current coming from the external inductor L1. The current

is monitored by the internal sense resistor Rsense to Set and Reset the flip–flop U3 and U6 according to the comparators U2 and U4 output state.

Figure 21. Basic DC/DC Boost Structure

#### **Output Load Drive**

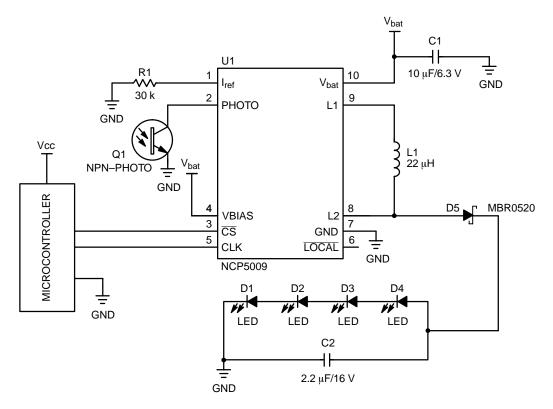

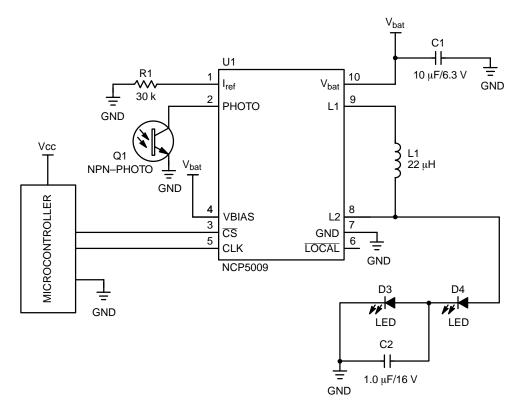

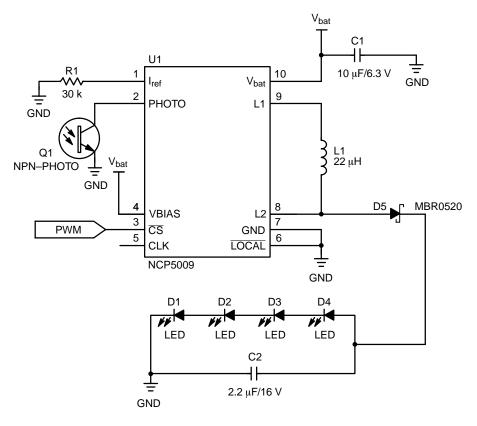

In order to make profit of the built—in Boost capabilities, one shall operate the NCP5008/NCP5009 in the continuous output current mode. Such a mode is achieved by using and external reservoir capacitor (preferably a low ESR ceramic type) across the LED as depicted in Figures 22, 23, 24, 25, and 26.

Using an extra photo sensor is not mandatory and the related pin 2 can be either left open or connected to  $V_{bat}$ , but must not be grounded on the NCP5009 version only.

At this point, the designer must carefully analyze two parameters:

1. The output voltage must be limited to 15 V maximum. It's the designer responsibility to make sure that spike voltages beyond the

- maximum rating will not exist across pin 8 and ground. Depending upon a specific application ( $V_{bat}$  voltage, PCB layout...), using an external voltage clamp could be necessary.

- 2. The peak current flowing into the LED diodes shall be within the maximum ratings specified for these devices.

The Schottky diode D5, associated with capacitor C2, provides a rectification and filtering function.

When a pulse-operating mode is acceptable:

- The LEDs brightness can be controlled in LOCAL mode with a PWM on  $\overline{\text{CS}}$  pin as depicted in Figure 24.

- Or the Schottky can be removed and replaced by at least one LED diode as depicted in Figure 23.

#### TYPICAL APPLICATION CIRCUIT

Figure 22. Basic DC Current Mode Operation in REMOTE Control

Figure 23. Typical Semi-Pulsed Mode of Operation in REMOTE Mode

Figure 24. PWM Current Control Mode Operation in LOCAL Mode

Figure 25. DAC Current Control Mode Operation in LOCAL Mode

Figure 26. Basic DC Current Mode Operation in LOCAL Mode

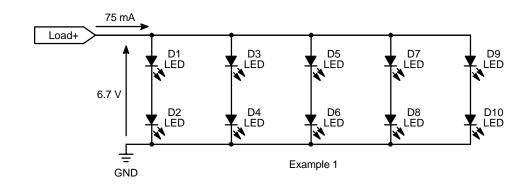

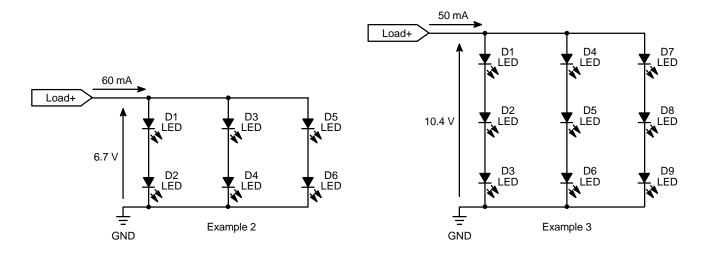

#### **TYPICAL LEDS LOAD MAPPING**

Figure 27. Three different examples of load can be driven by the NCP5009 or NCP5008 Condition:  $V_{bat}=3.6~V,~L=22~\mu H$

#### MANUFACTURER REFERENCE

| Design Ref | Value/Reference or Size | Manufacturer     | Ref #               |

|------------|-------------------------|------------------|---------------------|

| D5         | MBR0520/SOD-123         | ON Semiconductor | MBR0520             |

| L1         | 22 μΗ/1210              | muRata           | LQH3C220K34         |

| C1         | 10 μF/ 6.3 V/0805       | muRata           | GRM40 X5R 106K 6.3  |

| C2         | 2.2 μF/16 V/1206        | muRata           | GRM42-6 X7R 225K 16 |

| Q1         | SFH320/PLCC2            | Osram            | SFH320              |

| D1 to D4   | White LED               | Osram            | LW5413-VBW-1        |

#### **ORDERING INFORMATION**

| Device      | Operating Temperature Range | Package  | Shipping           | Marking |

|-------------|-----------------------------|----------|--------------------|---------|

| NCP5008DMR2 | −25°C top +85°C             | Micro 10 | 4000 Tape and Reel | 5T8     |

| NCP5009DMR2 | −25°C top +85°C             | Micro 10 | 4000 Tape and Reel | 5T9     |

#### LAYOUT EXAMPLE

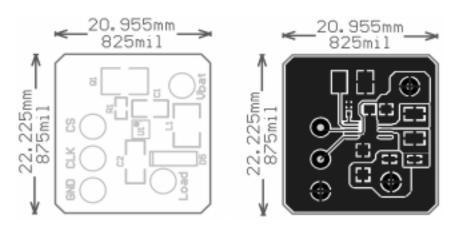

Figure 28. Typical Printed Circuit Layout (the Top Silk Screen and the Top Layer)

The Figure 28 represents the typical printed circuit layout based on the basic application Figure 1. This application has been routed on a single copper layer to save cost. A dual side PCB has better noise protection and can be the right choice for an industrial system. In order to avoid voltage spikes, care must be observed to group the capacitors, the inductor, the Schottky diode and the

integrated circuit in the same area. On the other hand, using large copper tracks to reduce the resistor connectivity is strongly recommended.

Obviously, the connectors GND, CLK,  $\overline{\text{CS}}$ ,  $V_{\text{bat}}$  and Load are for engineering purpose only and not for final application.

#### **PACKAGE DIMENSIONS**

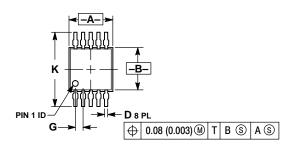

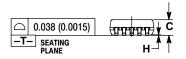

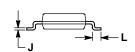

Micro 10 **DM SUFFIX** CASE 846B-02 **ISSUE B**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION "A" DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION "B" DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.101) PER SIDE.

5. 846B-01 OBSOLETE. NEW STANDARD 846B-02

|     | MILLIN | METERS | S INCHES  |       |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 2.90   | 3.10   | 0.114     | 0.122 |  |

| В   | 2.90   | 3.10   | 0.114     | 0.122 |  |

| С   | 0.95   | 1.10   | 0.037     | 0.043 |  |

| D   | 0.20   | 0.35   | 0.008     | 0.014 |  |

| G   | 0.50   | BSC    | 0.020 BSC |       |  |

| Н   | 0.05   | 0.15   | 0.002     | 0.006 |  |

| 7   | 0.10   | 0.21   | 0.004     | 0.008 |  |

| K   | 4.75   | 5.05   | 0.187     | 0.199 |  |

| Ĺ   | 0.40   | 0.70   | 0.016     | 0.028 |  |

ON Semiconductor and U are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4-32-1 Nishi-Gotanda, Shinagawa-ku, Tokyo, Japan 141-0031

Phone: 81-3-5740-2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.